Five of the largest semiconductor vertical markets are combining to drive several of the widest industry trends: unending growth in design complexity and size, proliferation of peripherals, increase in computing power, surging I/O traffic activity, and a critical need to contain the otherwise escalating energy consumption. The cumulative effects of these trends impact dramatically the design verification landscape and foster widespread adoption of hardware emulation platforms.

The five verticals contributing to these trends are data center networking, communication/5G, autonomous driving (AD), storage, and artificial intelligence (AI) & machine learning (ML).

A brief history of hardware-assisted verification

According to the ESD Alliance, a SEMI Technology Community, the hardware-assisted verification (HAV) market has grown haltingly since 1995, lagging behind hardware description language (HDL) simulation with a gap exceeding $200 million for the entire 2000-2010 decade. Starting in 2011, a surge in HAV revenues closed the gap, only to reopen and widen again from 2014.

In 2018, a new reality reversed the gap in favor of HAV tools. The ESD Alliance reported a 2020 record revenue for HAV tools in the amount of $718 million. See Table # 1.

It is reasonable to assume that the drive to embrace hardware-assisted verification from the five critical markets will continue and accelerate in the foreseeable future.

SPONSORED | Cervoz SSD overcomes the challenges facing in-vehicle applications

Trends and verification challenges in data center networking, communication/5G, AD, AI/ML, and storage markets underline how leading-edge hardware emulators — the largest contributor to the HAV market —can address them. Power trends and power analysis are briefly discussed in the last section.

Data center networking

Data center networking enjoyed explosive growth sustained by new applications, such as software-defined networking (SDN). Emerging protocols that include 5G, time-sensitive networking (TSN), and automotive internet played a role as well. All contribute to an expanded port count, now exceeding 256, increased port speeds approaching 800Gb/sec, enlarged bandwidth, and lowered latencies. The consequence is exploding design sizes into multi-billion equivalent gates, and daunting pre-silicon design verification due to shrinking time allocation to ensure that performance and power budgets are met.

Hardware Emulation for Networking

To meet the challenges, a leading-edge hardware emulator must possess three traits: platform, applications, and ecosystem.

(Image source: Siemens EDA)

As for the platform, its capacity must reach 15 billion gates with scalability starting at one billion gates, while maintaining consistent speed of execution across all configurations. It ought to support ternary content-addressable memories (TCAMs) natively to avoid cumbersome and inefficient modeling. Equally important, the communication channel between the test environment and the device under test (DUT) running in the emulator must exhibit wide bandwidth and low latency to accommodate the increasing number of ports.

As for applications, both in-circuit emulation (ICE) and virtual deployment are necessary. Deterministic debugging is a must for ICE, and a rich set of speed adapters is essential. For virtual mode, an expanded library of proven virtual solutions (such as VirtuaLAB Ethernet and VirtuaLAB PCIe from Siemens) is mandatory.

Communications and 5G

Two characteristics of the communication market, specifically 5G applications, stand out. First, a stream of about 50,000 5G patents in 2018 demonstrates deployment acceleration. Second, specialized semiconductor content is required to meet low power, performance, size, and latency, across a range of applications such as smart devices and cities, IoT edge products, virtual reality, digital industry applications, virtual reality, and autonomous driving vehicles.

Hardware Emulation for 5G

To address 5G design verification, a comprehensive, end-to-end suite of tools integrated in a flow that starts at the pre-silicon intellectual property (IP) level and proceeds all the way to the post-silicon test lab is a necessity.

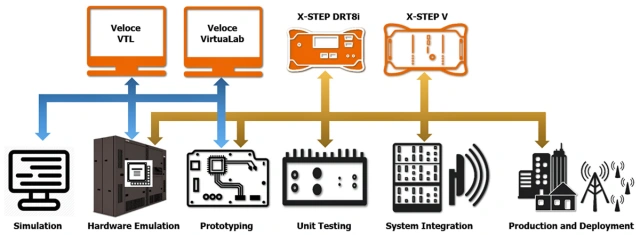

In a complete verification/validation cycle, the flow encompasses simulation, emulation, prototyping, unit testing, system integration, and post-silicon testing. Simulation is aimed at IP/block-level verification. Hardware emulation takes over from simulation to perform sub-system verification and, in combination with FPGA prototyping, verifies and validates the full system including software through tape-out. A well-integrated suite of emulation and prototyping platforms can share the same stimulus and verification setup from end to end.

Autonomous driving

AD designs involve several critical issues from safety and security concerns to avoid liabilities to big data processing that require massive communication between vehicle and cloud computing.

Verification challenges stem from the growing number of sensors that may exceed 50 various types, the increasing amount of software, now reaching 100 million lines of code, and the hardware and software complexity that must be validated together. This requires a vast amount of verification cycles to certify that an autonomous driving car is safe and secure.

Hardware Emulation for AD

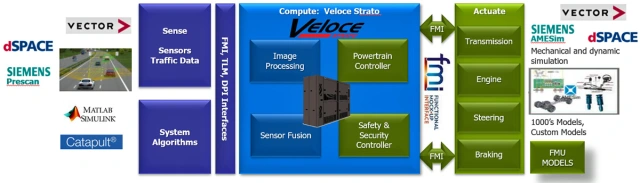

Verification/validation of an AD controller must deal with sense, compute, and actuate. Sense collects sensory information to capture driving scenarios. Compute performs algorithmic processing of those scenarios to formulate a decision. Action acts on those decisions by sending commands to the engine, transmission, steering and braking system, calling for integration of several technologies. Hardware emulation computes the sensor data generated by a virtual environment like VECTOR CANoe, dSPACE, or Siemens Pre-Scan, and generates actions to be sent to actuate implementation via functional models for the engine and steering wheel, such as Siemens AMESim, and others.