A hardware emulator provides enough power to keep the design for testability (DFT) verification schedule on track, increasing yields and ultimately boosting profits

Source: Design News

The development cycle of an integrated circuit (IC) –– or informally, chip –– from the conceptual stage to production and shipping to end-users involves several stages. One metric to measure the length of the cycle is the time to market (TTM) that stops when the chip leaves the factory. Missing TTM is a dreadful event that may jeopardize the success of the chip and possibly the future of the company. Meeting the TTM schedule does not ensure a revenue flow from selling it, either. That metric is known as the time to entitlement (TTE). Even if the TTM is on schedule, missing the TTE can pose serious problems for the vendor.

Consider the case of a system house purchasing a batch of chips and subjecting them to an incoming inspection. Should the inspection fail, no revenue would flow to the vendor. If the inspection succeeds, but the chip fails in the field once installed in a product, the relationship between vendor and customer would be compromised forever.

Thorough IC testing before shipping may be a challenge to the TTM but helps TTE.

Recent statistics reveal that the cost of testing a batch of chips after manufacturing to determine which parts are free of manufacturing defects (as opposed to free from design bugs), adds up to 40% to the cost of building the chip.

Each of these considerations drives the electronics industry to devise methods to build testability into the chip at the design stage to lower testing costs and increase product quality.

The methodology that makes this possible is known as Design for Testability (DFT) and can:

- Ensure the detection of all faults in a circuit to increase the quality of the product and accelerate TTE

- Reduce the cost and time associated with test development to improve manufacturing economies and accelerate the TTM

- Decrease execution time of testing fabricated chips, accelerating the TTM

DFT is usually incorporated in the design at the gate level after it has been verified to be functionally correct before taping out the netlist to the foundry. Unfortunately, the insertion of the on-chip test infrastructure may compromise its functional integrity, making it essential to perform a gate-level verification of the design after the DFT implant. The netlist size after insertion increases dramatically, stretching the time to verification way beyond an already compressed TTM schedule.

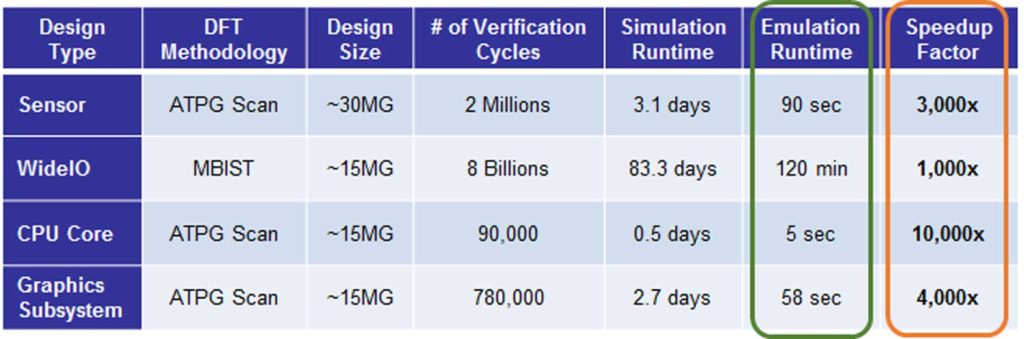

Given the level of design complexity, gate-level simulation –– the traditional go-to verification tool –– would require many months, if not years, for thorough and complete verification. Instead, this task is a perfect match for a hardware emulation platform. Only hardware emulation can verify the chip functionality, regardless of its size and complexity to more than a billion ASIC-gates capacity, performing at several orders of magnitude faster speed than simulation. While all hardware emulators today support the speed and capacity for the job, only emulators based on custom silicon provide the 100% visibility of each node in the design necessary for failure analysis.

Emulation with a DFT App

A new DFT “app” is available for hardware emulation to fully verify a design-under-test (DUT) that

includes implanted DFT within an already constrained schedule. It brings two changes to the usage of a hardware emulator –– a change in the compilation flow and a change in run-time execution.

First, the hardware emulation’s compiler reads a gate-level design instrumented with the DFT structure together with a IEEE Standard Test Interface Language (STIL) format file including design I/O configuration, clock information and test vectors. The compiler creates an infrastructure for reading test vectors from the STIL file.

While hardware emulation performs at orders of magnitude faster speed than simulation, the DFT App verifies DFT patterns by four or five orders of magnitude. In practical terms, three-months-worth of simulation, or 2,160 hours, can be accomplished in less than an hour.